[ad_1]

在上下文中: AMD 于上月底推出了 Ryzen 9 7950X3D,并欢迎对其第二代 3D V-Cache 的热烈反响,尽管对其在 16 核 CPU 中的实用性有不同的看法。 现在他们已经分享了一些解释其性能的技术细节。

AMD 于 2019 年开始混合节点,当时它使用 7 纳米节点作为核心复合管芯 (CCD),将 12 纳米节点用于 Zen 2 微架构的 IO 管芯。 AMD 最近向 Tom’s Hardware 证实,Zen 4 将其升级到三个节点:CCD 的 5 nm 节点、IO 芯片的 6 nm 节点和 V-Cache 的 7 nm 节点。

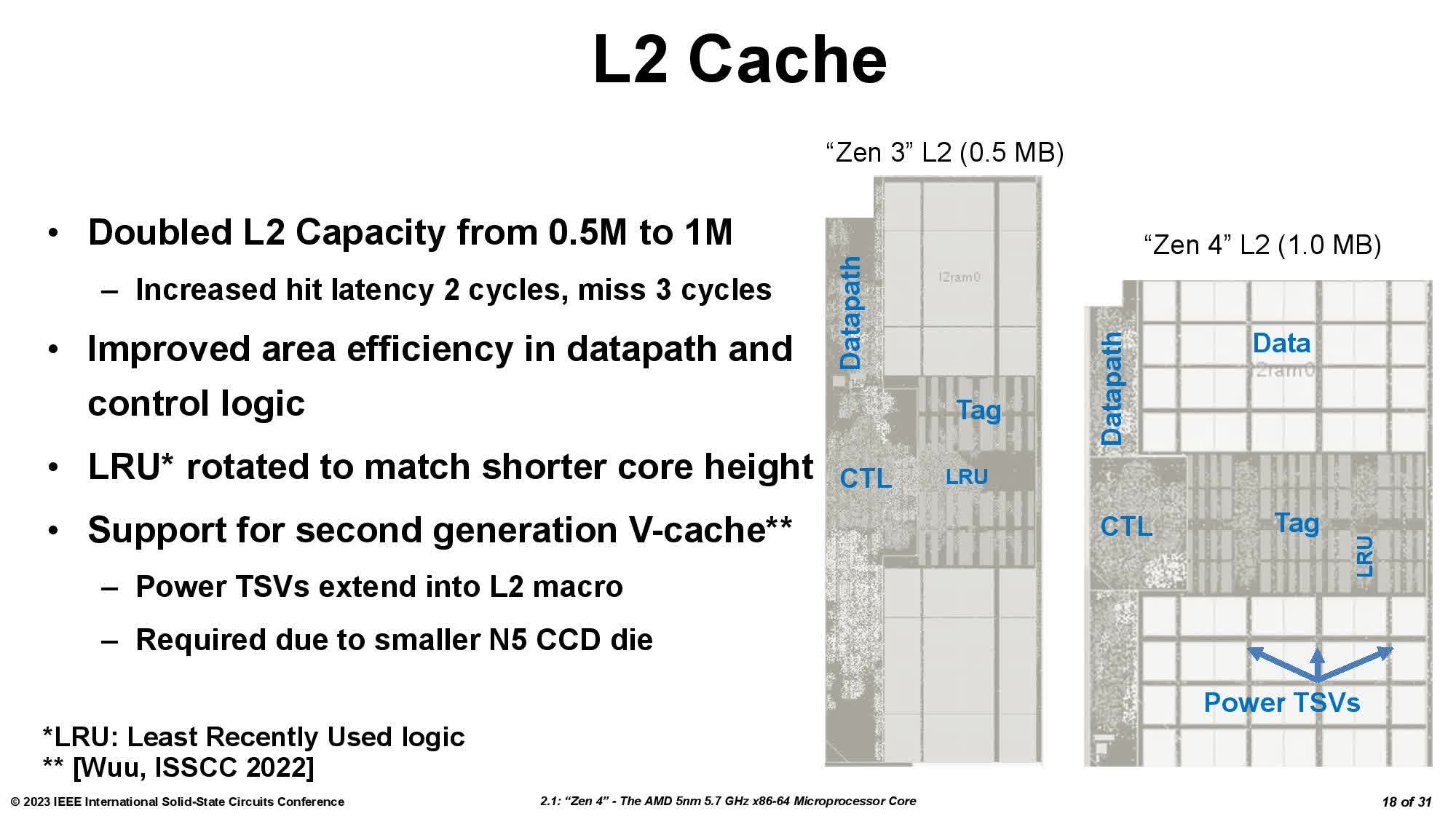

在最近的 ISSCC 演示中,AMD 解释了将一个节点堆叠到另一个节点所面临的一些挑战。 7950X3D 和原始的 5800X3D 都将其 V-Caches 置于其常规 L3 缓存之上,以允许它们进行连接。 这种安排还使 V-Cache 远离内核产生的热量。 然而,虽然 V-Cache 恰好位于 5800X3D 中的 L3 缓存之上,但它与 7950X3D 中内核边缘的 L2 缓存重叠。

部分问题是 AMD 将每个内核中的 L2 缓存数量从 Zen 3 中的 0.5 MB 增加到 Zen 4 中的 1 MB。但它通过在 L2 缓存中打孔用于硅通孔来解决额外的空间限制(TSV) 为 V-Cache 供电。 信号 TSV 仍然来自 CCD 中心的控制器,但 AMD 也对其进行了调整,将其占地面积减少了 50%。

AMD 将 V-Cache 从 41 毫米缩小2个 至 36 毫米2个 但保持相同的 4.7 B 晶体管。 台积电在专为 SRAM 开发的新版 7 纳米节点上制造缓存。 因此,尽管 CCD 是在更小的 5 nm 节点上制造的,但 V-Cache 每平方毫米的晶体管数比 CCD 多 32%。

AMD 实施的所有改进和变通办法总计将带宽增加 25% 至 2.5 TB/s,并提高了效率,但未具体说明。 第一代和第二代补充小芯片之间的九个月时间还不错。 希望它能在一个月后 Ryzen 7 7800X3D 到货时显示出它的价值。

[ad_2]

Source link